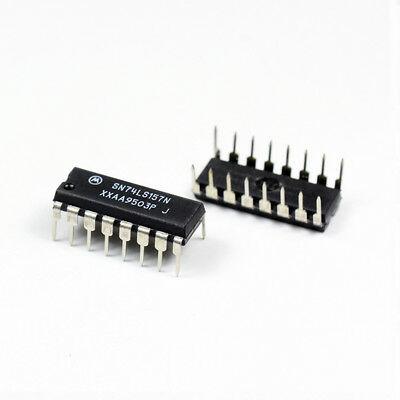

74LS107 (Dual JK flip-flop)

-

Sale

- Regular price 4 QAR

Product ID: VT-1426

30+ in stock

![]()

- Description

- Specifications

- Documents

- Reviews

- Questions & Answers

Description

The '107 contain two independent J-K flip-flops with individual J-K, clock, and direct clear inputs. The '107 is a positive pulse-triggered flip-flop. The J-K input data is loaded into the master while the clock is high and transferred to the slave and the outputs on the high-to-low clock transition. For these devices the J and K inputs must be stable while the clock is high.

Specifications

- Channels (#) 2

- Technology Family LS

- VCC (Min) (V) 4.75

- VCC (Max) (V) 5.25

- Input type TTL

- Output type TTL

- Clock Frequency (MHz) 30

- ICC (Max) (uA) 6000

- IOL (Max) (mA) 8

- IOH (Max) (mA) -0.4

- Features Negative edge triggered, High speed (tpd 10-50ns), Clear

Documents

Reviews

Questions & Answers